TPS-VU29P HLS

Empowering Large-Scale SoC Innovation with Scalable Capacity and Intelligent Control.

High-Speed GTM (PAM4)

Equipped with QSFP56 high-speed interfaces, supporting 56Gbps per channel to meet next-generation high-bandwidth demands.

Advanced Connectivity

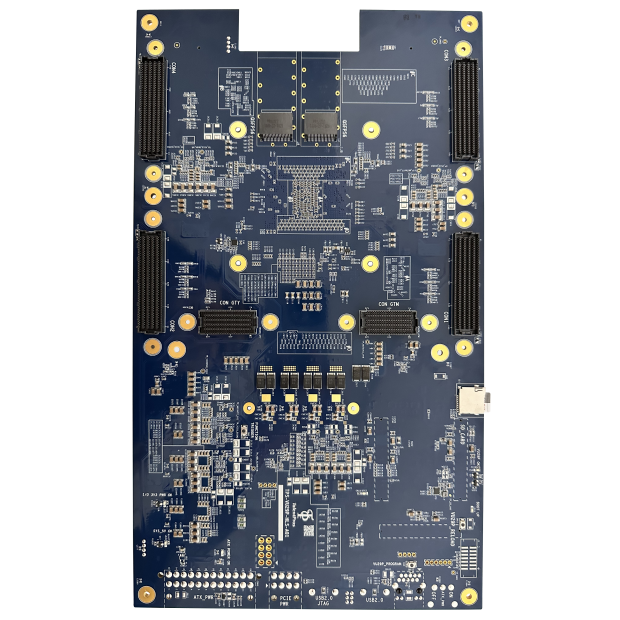

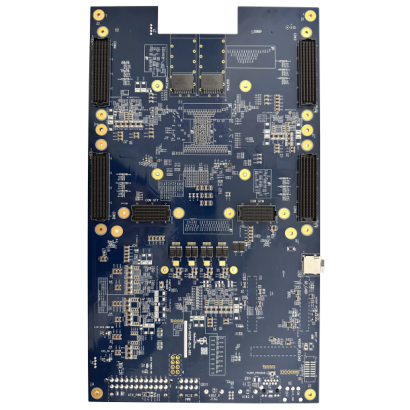

Provides up to 652 HP IOs and a dual-transceiver architecture (GTY/GTM), demonstrating ultimate system integration flexibility.

Smart Management

Integrated smart management center supports remote deployment and Self-Test, ensuring development workflow stability.

High-Speed Transmission, Setting New Benchmarks for SoC Verification

The TPS-VU29P HLS is designed specifically for communication and data center applications. By integrating GTM (PAM4) technology, we achieve exceptionally high data throughput within a compact hardware footprint. With superior High-speed signal integrity capabilities, this platform enables R&D teams to conduct precise verification in even the most demanding signal environments, significantly optimizing the product's Time-to-market.

- Superior Data Processing: Powered by XCVU29P FPGA, featuring 3,780K system logic cells and 454.5Mb of internal memory resources.

- Hybrid Transceiver Architecture: Built-in 16-channel GTY (16 Gbps) and 16-channel GTM (56 Gbps) to meet diverse speed requirements.

- Smart Protection Mechanism: Automatically monitors voltage and temperature with built-in auto-shutdown to prevent hardware damage from overheating or voltage anomalies.

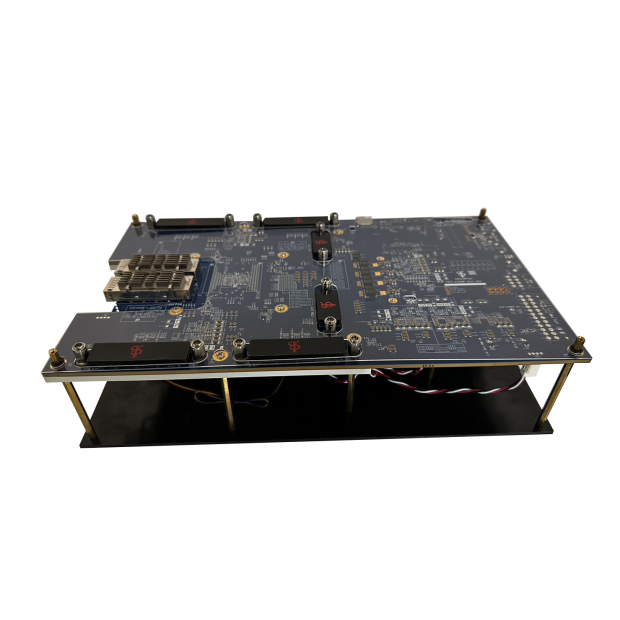

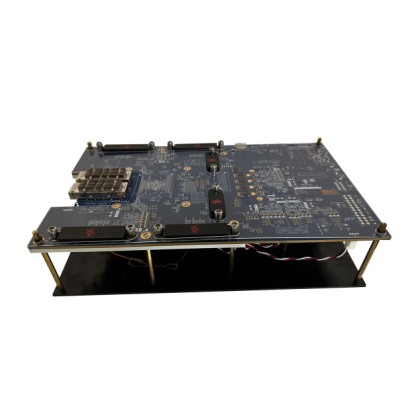

- PoC & Field Application: Lightweight "Lite" mechanical design lowers deployment barriers, making it an ideal tool for live demonstrations and Proof of Concept (PoC).

Standard Configuration

Built-in standard industrial interfaces to optimize data access, programming, and debugging efficiency:

Enterprise Security

Supports hardware-level AES-Key 256-bit encryption to ensure absolute confidentiality for core IP development:

Technical Specifications

| TPS-VU29P HLS Hardware Resources | |

|---|---|

| Process Technology | 16nm Virtex UltraScale+ Architecture |

| System Logic Cell | 3,780 K |

| VCCINT Core Power | 200A |

| Internal Memory | 454.5 Mb (Block RAM: 94.5Mb, Ultra RAM: 360Mb) |

| Transceivers Max Rate | GTM: 56 Gbps (PAM4) / GTY: 16 Gbps |

| HP IO Count | 652 |

| GTY Transceivers | 16 (TX/RX) |

| GTM Transceivers | 16 (TX/RX) |

| PCIe Compatibility | Gen4 / Gen3 Supported |

| MIPI D-PHY | 1.5 Gbps |

Ready to Accelerate Your Innovation?

Detailed datasheets and technical documentation are available upon request.

Please contact our team for more information regarding the TPS-VU29P-HLS.